# Vertically stacked multilayer atomiclayer-deposited sub-1-nm In<sub>2</sub>O<sub>3</sub> fieldeffect transistors with back-end-of-line compatibility <sup>6</sup>

Cite as: Appl. Phys. Lett. **120**, 202104 (2022); https://doi.org/10.1063/5.0092936 Submitted: 24 March 2022 • Accepted: 28 April 2022 • Published Online: 16 May 2022

🗓 Zhuocheng Zhang, Zehao Lin, 🗓 Mengwei Si, et al.

# **COLLECTIONS**

F This paper was selected as Featured

#### **ARTICLES YOU MAY BE INTERESTED IN**

Atomically thin  $In_2O_3$  field-effect transistors with  $10^{17}$  current on/off ratio Applied Physics Letters 119, 263503 (2021); https://doi.org/10.1063/5.0075166

Oxygen vacancy concentration as a function of cycling and polarization state in TiN/  $Hf_{0.5}Zr_{0.5}O_2/TiN$  ferroelectric capacitors studied by x-ray photoemission electron microscopy

Applied Physics Letters 120, 202902 (2022); https://doi.org/10.1063/5.0093125

Enhancement-mode atomic-layer thin In<sub>2</sub>O<sub>3</sub> transistors with maximum current exceeding 2 A/mm at drain voltage of 0.7 V enabled by oxygen plasma treatment Applied Physics Letters 118, 052107 (2021); https://doi.org/10.1063/5.0039783

☐ QBLOX

Shorten Setup Time

Auto-Calibration

More Qubits

Fully-integrated

Quantum Control Stacks

Ultrastable DC to 18.5 GHz

Synchronized <<1 ns

Ultralow noise

visit our website >

# Vertically stacked multilayer atomic-layer-deposited sub-1-nm In<sub>2</sub>O<sub>3</sub> field-effect transistors with back-end-of-line compatibility •

Cite as: Appl. Phys. Lett. **120**, 202104 (2022); doi: 10.1063/5.0092936 Submitted: 24 March 2022 · Accepted: 28 April 2022 · Published Online: 16 May 2022

Zhuocheng Zhang,<sup>1,2</sup> D Zehao Lin,<sup>1,2</sup> Mengwei Si,<sup>1,2</sup> D Di Zhang,<sup>3</sup> D Hongyi Dou,<sup>3</sup> Zhizhong Chen,<sup>1,2</sup> D Adam Charnas,<sup>1,2</sup> D Haiyan Wang,<sup>3</sup> D and Peide D. Ye<sup>1,2,a)</sup> D

#### **AFFILIATIONS**

- <sup>1</sup>Elmore Family School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana 47907, USA

- <sup>2</sup>Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana 47907, USA

- School of Materials Engineering, Purdue University, West Lafayette, Indiana 47907, USA

#### **ABSTRACT**

In this work, we demonstrate vertically stacked multilayer sub-1-nm  $\rm In_2O_3$  field-effect transistors (FETs) with surrounding gate in a backend-of-line (BEOL) compatible low-temperature fabrication process. A typical bottom-gated single layer  $\rm In_2O_3$  FET with maximum on-state current ( $\rm I_{ON}$ ) of 890  $\mu\rm A/\mu m$  at  $\rm V_{DS}=0.8~V$  and an on/off ratio over  $\rm 10^6$  is achieved with a channel length ( $\rm L_{ch}$ ) of 100 nm. The effects of HfO2 capping and O2 annealing are systematically studied, which is critical to realizing the multilayer FETs. Each atomically thin  $\rm In_2O_3$  channel layer with a thickness ( $\rm T_{IO}$ ) of 0.9 nm is realized by atomic layer deposition (ALD) at 225 °C. Multilayer FETs with a number of  $\rm In_2O_3$  layers up to 4 and 1.2 nm-thick HfO2 between each individual layer are fabricated. An enhancement of on-state current ( $\rm I_{ON}$ ) from 183  $\mu\rm A$  in a single layer  $\rm In_2O_3$  FET to 339  $\mu\rm A$  in a 4 layer device with an on/off ratio of  $\rm 3.4 \times 10^4$  is achieved, demonstrating the key advantage of the multilayer FETs to improve the current. Several critical features, such as large-area growth, high uniformity, high reproducibility, ultrathin body, flexibility, and BEOL compatibility, have turned ALD  $\rm In_2O_3$  into a noteworthy candidate for next-generation oxide semiconductor channel materials.

Published under an exclusive license by AIP Publishing. https://doi.org/10.1063/5.0092936

Exploration for back-end-of-line (BEOL) compatible next-generation channel materials is becoming crucial for monolithic 3D integration at advanced technology nodes. Oxide semiconductors, as one competitive candidate, have been widely studied over the past few decades and become the leading material in the field of flat panel displays due to three main advantages. First, the high transparency due to the large bandgap of oxide semiconductors enables numerous applications in flexible displays and wearable devices. Second, the amorphous microstructure makes oxide semiconductors film relatively uniform and avoids variation of electrical properties caused by grain boundary problems in poly-Si thin film transistors (TFTs). Third, the bottom of the conduction band in amorphous oxide semiconductors is primarily composed of the isotropically spread metal *ns* orbitals, which has possible direct overlap with neighboring metal *ns* orbitals, so the chemical bond is insensitive to distortion and the mobility is

much higher than covalent semiconductors consisting of  $sp^3$  orbitals with strong directivity.<sup>8</sup>

Nevertheless, the large film thickness by sputtering and the lack of effective gate control due to the degeneracy in the conduction band have impeded oxide semiconductors to be used as active channel materials in ultra-scaled TFTs. Remarkably, recent atomic layer deposition (ALD) deposited nanometer-thin  $\rm In_2O_3$  field-effect transistors (FETs) exhibit maximum on-state currents over 2 mA/ $\mu m$  and well-behaved switching characteristics with the on/off ratio over  $10^6$  and the minimum subthreshold slope (SS) of 88 mV/dec. Compared to the most sputtered oxide semiconductor thin films, the emerging ALD channel offers two main advantages. First, ALD has an accurate film thickness control in atomic scale and high reproducibility. Second, ALD provides large-area uniformity and excellent conformity on 3D structures. Hence, carrier scattering due to surface roughness can

a) Author to whom correspondence should be addressed: yep@purdue.edu

be reduced with the atomically smooth surface of the In<sub>2</sub>O<sub>3</sub> thin film enabled by ALD. On the other hand, it has been confirmed that the ALD deposited In<sub>2</sub>O<sub>3</sub> has a strong thickness-dependent electron transport, which is attributed to the quantum confinement effect on the alignment of trap neutral level (TNL). 13,14 The bandgap increases from 1.4 eV in bulk In2O3 to 2.43 eV in a 0.7 nm-thick film as the thickness decreases, which is smaller than most other semiconductors of which the bandgap is usually larger than 3 eV.14 Therefore, the lack of gate control due to extremely high carrier density can be solved by lowering the film thickness and a maximum on-state current (I<sub>ON</sub>) of 2.5 mA/ $\mu$ m with a high field effect mobility ( $\mu$ <sub>FE</sub>) of 113 cm²/V⋅s has been reported in recent back-gate In<sub>2</sub>O<sub>3</sub> FETs with a channel thickness of 2.2 nm and a channel length of 40 nm. 15 In addition, an enhancement-mode operation is also achieved through O<sub>2</sub> plasma or low temperature O<sub>2</sub> annealing because of the filling of oxygen vacancies, 16,17 making the ALD deposited In<sub>2</sub>O<sub>3</sub> film a choice as the channel material in the complementary metal-oxide-semiconductor (CMOS) design and BEOL compatible monolithic 3D integration.

In this work, we systematically study the effects of  $HfO_2$  capping and  $O_2$  annealing to effectively control the threshold voltage  $(V_T)$  of each channel layer based on typical atomically thin  $In_2O_3$  FETs with  $I_{\rm ON}$  of 890  $\mu A/\mu m$  at  $V_{\rm DS} = 0.8$  V, the on/off ratio over  $10^6$ , the channel thickness  $(T_{\rm IO})$  of 2 nm, and the channel length  $(L_{ch})$  of 100 nm. Vertically stacked multilayer sub-1-nm-thin  $In_2O_3$  FETs with surrounding gate with the dielectric of 5 nm  $HfO_2$  are realized with an

enhancement of  $I_{\rm ON}$  as the number of  $In_2O_3$  channel layers increases, demonstrating the key advantage of multilayer FETs.

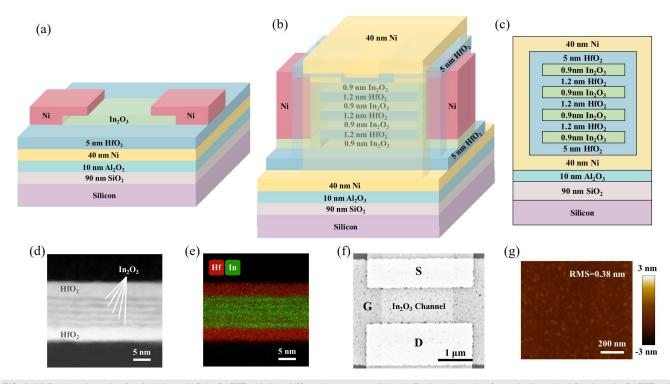

Figure 1(a) shows the schematic diagram of a single layer In<sub>2</sub>O<sub>3</sub> FET grown by ALD. The gate stack includes 40 nm Ni as the bottom gate and 5 nm HfO<sub>2</sub> as the gate dielectric. Figure 1(b) shows the 3D schematic diagram of a stacked four-layer In<sub>2</sub>O<sub>3</sub> FET with 0.9 nm In<sub>2</sub>O<sub>3</sub> as each semiconducting channel separated by 1.2 nm HfO<sub>2</sub>. Figure 1(c) shows the cross-sectional view of the device schematic in source/drain direction. Thickness of films is accurately controlled by ALD cycles and measured by ellipsometry. The whole vertically stacked channel is surrounded by 40 nm Ni as gate metal and 5 nm HfO<sub>2</sub> as gate dielectric so that all inner In<sub>2</sub>O<sub>3</sub> channels can be modulated by the surrounding gate. The detailed device fabrication process is described in the supplementary material. Figure 1(d) shows the scanning transmission electron microscopy (STEM) image of a stacked five-layer In<sub>2</sub>O<sub>3</sub> structure with clear interfaces between In<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>. Figure 1(e) shows the energy dispersive x-ray spectroscopy (EDS) image of the same stack, which also confirms the multilayer structure. Figure 1(f) shows the scanning electron microscopy (SEM) image of a typical fabricated device with sharp edge and well-defined  $L_{ch}$  of 1  $\mu$ m. All devices have a channel width of 2  $\mu$ m. Figure 1(g) shows a low surface roughness of 0.38 nm for the ALD deposited In<sub>2</sub>O<sub>3</sub> film measured by atomic force microscope (AFM). This result has relatively small variance for different batches of ALD In<sub>2</sub>O<sub>3</sub> films, indicating high reproducibility in potential large-scale industrial manufacture. The fabrication of vertically stacked multilayer In2O3 FETs

FIG. 1. (a) Device schematic of a single-layer ALD  $In_2O_3$  FET with 5 nm  $HfO_2$  as bottom gate dielectric. Device schematic of a vertically stacked four-layer  $In_2O_3$  FET with 5 nm  $HfO_2$  as surrounding gate dielectric in (b) a 3D model, (c) cross-sectional view in the S/D direction. (d) STEM image and (e) EDS image of the vertically stacked five-layer ALD  $In_2O_3$  structure. (f) SEM image (top view) of a finished vertically stacked multilayer  $In_2O_3$  FET with surrounding gate. (g) AFM measurement of 2 nm  $In_2O_3$  thin film deposited on a Si substrate with a surface roughness (RMS) of 0.38 nm.

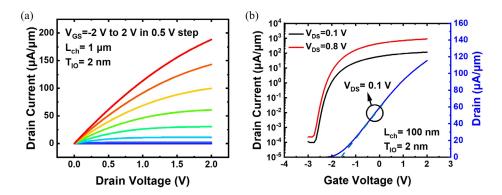

**FIG. 2.** (a) Output characteristics of a single layer  $\ln_2 O_3$  FET with 5 nm  $\text{HfO}_2$  as bottom gate dielectric and channel length of 1  $\mu\text{m}$ . (b) Transfer characteristics of a single layer  $\ln_2 O_3$  FET with 5 nm  $\text{HfO}_2$  as bottom gate dielectric and channel length of 100 nm, showing  $\text{I}_{\text{ON}}$  of 890  $\mu\text{A}/\mu\text{m}$  at  $\text{V}_{\text{DS}} = 0.8 \, \text{V}$ .

has a low thermal budget of  $250\,^{\circ}$ C, which is in general BEOL compatible for monolithic 3D integration.

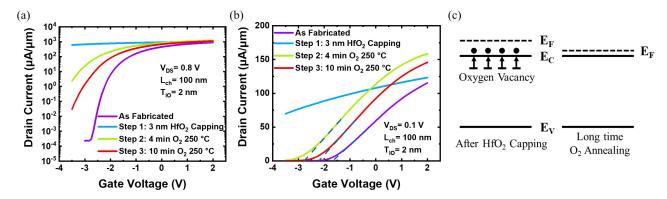

Figure 2 shows the typical output and transfer characteristics of the bottom-gated single layer In<sub>2</sub>O<sub>3</sub> FET with T<sub>IO</sub> of 2 nm. Drain current saturation is observed at large  $V_{DS}$  in the device with  $L_{ch}$  of 1  $\mu$ m. Maximum  $I_{ON}$  of 890  $\mu$ A/ $\mu$ m at  $V_{DS} = 0.8$  V, the on/off ratio over  $10^6$ , the subthreshold slope (SS) of 130 mV/dec, and  $\mu_{\rm FE}$  of 23 cm<sup>2</sup>/V·s are achieved in the single layer In<sub>2</sub>O<sub>3</sub> FET with L<sub>ch</sub> of 100 nm. To investigate the conducting mechanism of the ALD deposited In<sub>2</sub>O<sub>3</sub> films, Fig. 3 presents the evolution of the transfer characteristics of the same single layer In<sub>2</sub>O<sub>3</sub> FET after HfO<sub>2</sub> capping and multiple times of O<sub>2</sub> annealing in (a) log-scale plot at  $V_{DS} = 0.8$  V and (b) linear-scale plot at  $V_{DS} = 0.1 \text{ V}$ . A loss of gate control over the  $In_2O_3$  channel is observed after 3 nm HfO<sub>2</sub> capping by ALD on the as-fabricated device at 200 °C, whereas the control is gradually retrieved after following O2 annealing at 250 °C with clear positive V<sub>T</sub> shift. Such phenomena can be understood by the band diagram of In<sub>2</sub>O<sub>3</sub> shown in Fig. 3(c). It is known that oxygen vacancies act as shallow donors and determine the carrier density in In<sub>2</sub>O<sub>3</sub> related films. <sup>16–18</sup> Modulation of oxygen pressure during film deposition or thermal annealing contributing to the change in electrical conductivity has been widely investigated in ITO, In-Zn-O (IZO), In-Ga-Zn-O (IGZO), etc. 1-6,18,19 Therefore, it is likely that oxygen atoms in atomically thin In2O3 film are scavenged by the ALD growth of HfO2 due to a more stable Hf-O bond with a dissociation

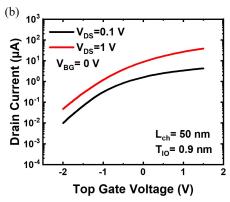

energy of 801 kJ/mol compared to In-O bond of 346 kJ/mol. 20,21 The created oxygen vacancies in In<sub>2</sub>O<sub>3</sub> provide extra electrons, and the Fermi level moves deeply into the conduction band, resulting in a large electron density, negative V<sub>T</sub> shift, and the lack of gate control. More defects can also be generated in the bulk film and interface. Conversely, oxygen vacancies can be filled and defects can be healed by O<sub>2</sub> annealing, which reduces the interface trap density and lowers electron density with increasing annealing time, moves Fermi level toward the conduction band edge, and gradually restores gate control. Further experiments on material characterization are still needed to validate this explanation. In addition, the different gate control capabilities between top and bottom gates in a dual-gated single layer In<sub>2</sub>O<sub>3</sub> FET are also studied in Fig. 4. The measurement was done by adjusting single top/bottom gate voltage with another grounded. A better gate control is obtained in bottom-gated control condition because the carrier density of In<sub>2</sub>O<sub>3</sub> under S/D contact can only be modulated by bottom gate, leading to favorably controlled contact resistance (R<sub>C</sub>). Meanwhile, the bottom In<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> interface has less oxygen vacancies than the top In<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> interface, since In-O chemical bond is weaker than Hf-O one so that the ALD growth of In<sub>2</sub>O<sub>3</sub> on top of HfO<sub>2</sub> cannot break the surface Hf-O bond of the bottom HfO2 film.

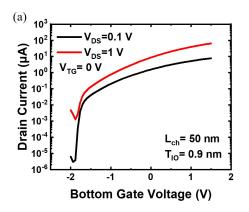

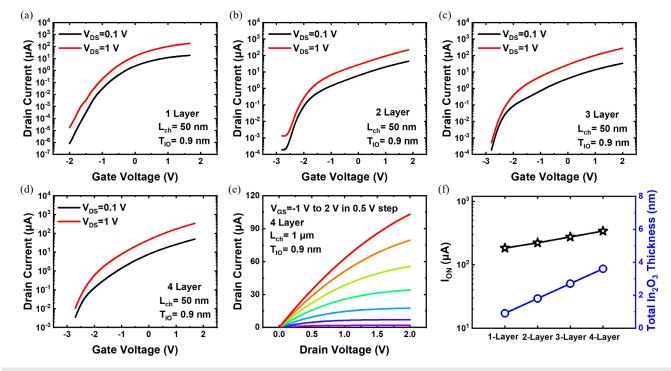

Figures 5(a)-5(d) present the transfer characteristics of stacked one, two, three, and four-layer  $In_2O_3$  FETs with  $L_{ch}$  of 50 nm and the surrounding gate structure shown in Fig. 1. Each  $In_2O_3$  channel layer

FIG. 3. (a) Logscale plot of the evolution of transfer characteristics of a bottom-gated single layer  $ln_2O_3$  FET with  $V_{DS} = 0.8$  V after HfO<sub>2</sub> capping and O<sub>2</sub> annealing. (b) Linear plot of the evolution of transfer characteristics of a bottom-gated single layer  $ln_2O_3$  FET with  $V_{DS} = 0.1$  V after HfO<sub>2</sub> capping and O<sub>2</sub> annealing. It shows the challenge of top-gate HfO<sub>2</sub> integration. (c) Band diagram of  $ln_2O_3$  after HfO<sub>2</sub> capping and long-time O<sub>2</sub> annealing showing the change of E<sub>F</sub>.

**FIG. 4.** (a) Transfer characteristics of a single layer  $\ln_2 O_3$  FET under bottom gate control with  $V_{TG}$  set to 0 V. (b) Transfer characteristics of a single layer  $\ln_2 O_3$  FET under top gate control with  $V_{BG}$  set to 0 V.

with  $T_{IO}$  of 0.9 nm is separated by 1.2 nm HfO<sub>2</sub>, and an on/off ratio around  $10^5$  is achieved. Figure 5(e) shows the output characteristics of a stacked four-layer  $In_2O_3$  FET with  $L_{ch}$  of 1  $\mu$ m, exhibiting drain current saturation at large  $V_{DS}$  as one-layer one shown in Fig. 2. Figure 5(f) summarizes  $I_{ON}$  at  $V_{DS} = 1$  V,  $V_{GS} = 1.7$  V and total  $In_2O_3$  channel thickness vs the number of vertically stacked layers. An increase in drain current is realized by stacking more  $In_2O_3$  channel layers, confirming that the key advantage of multilayer FETs for enhancing  $I_{ON}$  since multilayer FET is claimed by Si industry as the technology for 3 nm node and beyond. Nevertheless, a modest current gain from 183  $\mu$ A in a single layer  $In_2O_3$  FET to 339  $\mu$ A in a four-layer device is observed, which seems a limited enhancement for the stacked channel.

This is because the surrounding gate only has a relatively weak control of the inner second and third  $\rm In_2O_3$  channel compared to it can directly modulate the carrier density of first and fourth  $\rm In_2O_3$  channels over the top and bottom 5 nm-thick HfO2. Such deficiency can be improved by inserting gate metal between each  $\rm In_2O_3$  to achieve an equally strong gate control of all conducting channels. The nonlinear increase in  $\rm I_{ON}$  is due to a 200 nm  $\rm L_{ch}$  difference between top and the other  $\rm In_2O_3$  layers, which is a process issue with e-beam lithography and can be eliminated eventually.

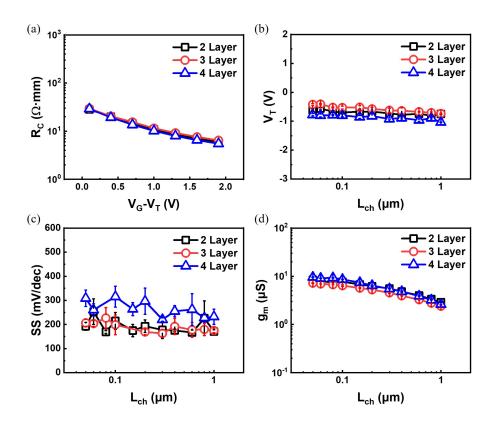

Figure 6(a) shows  $R_C$  extracted by the transfer length method (TLM) vs  $V_G - V_T$ .  $R_C$  is relatively large due to the sub-1-nm  $In_2O_3$  channel, which can be improved by increasing channel thickness or

**FIG. 5.** Transfer characteristics of a (a) single-layer, (b) two-layer, (c) three-layer, and (d) four-layer  $ln_2O_3$  FET with surrounding gate. (e) Output characteristics of a four-layer  $ln_2O_3$  FET with surrounding gate and channel length of 1  $\mu$ m. (f) On-state current at  $V_{DS}$  of 1 V,  $V_{GS}$  of 1.7 V and total  $ln_2O_3$  channel thickness vs number of layers, showing increasing current with more  $ln_2O_3$  layers.

**FIG. 6.** (a) Contact resistance vs  $V_G - V_T$  of stacked multilayer  $In_2O_3$  FETs. (b)  $V_T$ , (c) SS, and (d)  $g_m$  scaling metrics of stacked multilayer  $In_2O_3$  FETs with surrounding gate,  $L_{ch}$  from 50 nm to 1  $\mu$ m. Each data point represents the average of at least three devices.

raised S/D contacts. The device performance of multilayer FETs still has large room to improve by optimizing the fabrication process. Figures 6(b)–6(d) summarize the scaling metrics of stacked multilayer In<sub>2</sub>O<sub>3</sub> FETs with L<sub>ch</sub> from 50 nm to 1  $\mu$ m statistically. Each data point represents the average of at least three devices. Figure 6(b) shows V<sub>T</sub> vs L<sub>ch</sub>, which is extracted by the linear extrapolation method at V<sub>DS</sub>=0.1 V. Notably, the device has a strong immunity to short

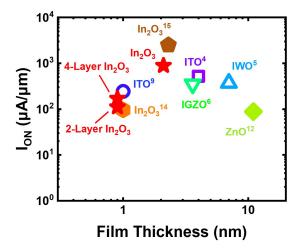

$\label{eq:FIG.7.} \textbf{FIG. 7.} \ \ \text{Benchmark of I}_{ON} \ \ \text{vs film thickness of recent thin film oxide semiconductor transistors.} \ \ \text{Solid symbols represent films grown by ALD.}$

channel effects due to the ultrathin In2O3 channel, whose thickness is even comparable to monolayers of 2D semiconductors, such as MoS<sub>2</sub>. Moreover, high-quality HfO2 gate dielectric can be realized by ALD on the 3D In<sub>2</sub>O<sub>3</sub> channel, while it is impeded by the lack of dangling bonds on the van der Waals surface in 2D materials. Both factors contribute to extremely small transistor characteristic length,<sup>22</sup> offering great potential for ultimately scaled FETs. Figure 6(c) presents SS vs L<sub>ch</sub> characteristics. Minimum SS of 163 mV/dec is obtained in a threelayer In2O3 FET, which can be further improved by improving interface quality and scaling gate dielectric. Figure 6(d) summarizes the intrinsic transconductance vs L<sub>ch</sub> for In<sub>2</sub>O<sub>3</sub> FETs with different channel layers. Figure 7 presents a benchmarking of ION for ALD In2O3 FETs and other sputtered oxide semiconductors. As can be seen, ALD deposited oxides have more accurate thickness control in sub-1-nm region compared to sputtered films. Meanwhile, the current level of the atomically thin ALD In<sub>2</sub>O<sub>3</sub> FETs can compete with other sputtered oxides with larger thickness, demonstrating outstanding performance of ALD In<sub>2</sub>O<sub>3</sub> as a promising BEOL-compatible oxide semiconductor channel.

In conclusion, BEOL-compatible vertically stacked multilayer  $\rm In_2O_3$  FETs with surrounding gate are demonstrated. Each atomic-layer-thin 0.9 nm  $\rm In_2O_3$  channel layer and 1.2 nm HfO2 separation layer are realized by accurately controlled ALD at 225 °C. Several distinct features, namely, large-area growth, high uniformity, excellent conformability, ultrathin body, and low thermal budget fabrication process demonstrate ALD  $\rm In_2O_3$  as a competitive oxide semiconductor channel material for future monolithic 3D integration and ultimately scaled electronics.

See the supplementary material for the details of device fabrication and characterization.

The authors gratefully acknowledge the funding support from Semiconductor Research Corporation (SRC) Nanoelectronic Computing Research Innovative Materials and Processes for Accelerated Compute Technologies Center and Defense Advanced Research Projects Agency/SRC Joint University Microelectronics Program Applications and Systems-driven Center for Energy Efficient integrated Nano Technologies Center on this work.

### **AUTHOR DECLARATIONS**

# **Conflict of Interest**

The authors have no conflicts to disclose.

# **DATA AVAILABILITY**

The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### REFERENCES

- <sup>1</sup>K. Nomura, A. Takagi, T. Kamiya, H. Ohta, M. Hirano, and H. Hosono, Jpn. J. Appl. Phys. 45(5B), 4303–4308 (2006).

- <sup>2</sup>H. Yabuta, M. Sano, K. Abe, T. Aiba, T. Den, H. Kumomi, K. Nomura, T. Kamiya, and H. Hosono, Appl. Phys. Lett. 89(11), 112123 (2006).

- <sup>3</sup>E. Fortunato, P. Barquinha, and R. Martins, Adv. Mater. 24(22), 2945–2986 (2012).

<sup>4</sup>S. M. Li, M. C. Tion, O. C. Coo, M. F. Wong, T. V. Li, O. L. Hu, V. F. Li, and V.

- <sup>4</sup>S. M. Li, M. C. Tian, Q. G. Gao, M. F. Wang, T. Y. Li, Q. L. Hu, X. F. Li, and Y. Q. Wu, Nat. Mater. **18**(10), 1091–1097 (2019).

- <sup>5</sup>W. Chakraborty, B. Grisafe, H. Ye, I. Lightcap, K. Ni, and S. Datta, paper presented at the 2020 IEEE Symposium on VLSI Technology, 2020.

- <sup>6</sup>S. Samanta, K. Han, C. Sun, C. Wang, A. V. Y. Thean, and X. Gong, paper presented at the 2020 IEEE Symposium on VLSI Technology, 2020.

- <sup>7</sup>T. Kamiya, K. Nomura, and H. Hosono, Sci. Technol. Adv. Mater. 11(4), 044305 (2010).

- <sup>8</sup>K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, Nature 432(7016), 488–492 (2004).

- <sup>9</sup>M. Si, J. Andler, X. Lyu, C. Niu, S. Datta, R. Agrawal, and P. D. Ye, ACS Nano 14(9), 11542–11547 (2020).

- <sup>10</sup> M. Si, Z. Lin, A. Charnas, and P. D. Ye, IEEE Electron Device Lett. **42**(2), 184–187 (2021).

- <sup>11</sup>J. Sheng, H.-J. Jeong, K.-L. Han, T. Hong, and J.-S. Park, J. Inf. Disp. 18(4), 159–172 (2017).

- <sup>12</sup>M. Wang, D. Zhan, X. Wang, Q. Hu, C. Gu, X. Li, and Y. Wu, IEEE Electron Device Lett. 42(5), 716–719 (2021).

- <sup>13</sup>P. D. Ye, J. Vac. Sci. Technol. A **26**(4), 697–704 (2008).

- <sup>14</sup>M. Si, Y. Hu, Z. Lin, X. Sun, A. Charnas, D. Zheng, X. Lyu, H. Wang, K. Cho, and P. D. Ye, Nano Lett. 21(1), 500–506 (2021).

- <sup>15</sup>M. Si, Z. Lin, Z. Chen, and P. D. Ye, in Proceeding of the 2021 IEEE Symposium on VLSI Technology, 2021.

- 16 A. Charnas, M. Si, Z. Lin, and P. D. Ye, Appl. Phys. Lett. 118(5), 052107 (2021).

- <sup>17</sup>M. Si, A. Charnas, Z. Lin, and P. D. Ye, IEEE Trans. Electron Devices 68(3), 1075–1080 (2021).

- <sup>18</sup>T. Kamiya and H. Hosono, NPG Asia Mater. **2**(1), 15–22 (2010).

- <sup>19</sup>S. Y. Park, J. H. Song, C. K. Lee, B. G. Son, C. K. Lee, H. J. Kim, R. Choi, Y. J. Choi, U. K. Kim, C. S. Hwang, H. J. Kim, and J. K. Jeong, IEEE Electron Device Lett. 34(7), 894–896 (2013).

- <sup>20</sup>H. Fujiwara, Y. Sato, N. Saito, T. Ueda, and K. Ikeda, IEEE Trans. Electron Devices 67(12), 5329–5335 (2020).

- <sup>21</sup>Y.-R. Luo, Comprehensive Handbook of Chemical Bond Energies (CRC Press, 2007).

- 22 Y. Liu, X. D. Duan, H. J. Shin, S. Park, Y. Huang, and X. F. Duan, Nature 591(7848), 43–53 (2021).